# **USER MANUAL**

# Accessory 24E2A

**UMAC Axis Expansion Board**

4Ax-603398-xUxx

9/24/2015

### **Copyright Information**

© 2015 Delta Tau Data Systems, Inc. All rights reserved.

This document is furnished for the customers of Delta Tau Data Systems, Inc. Other uses are unauthorized without written permission of Delta Tau Data Systems, Inc. Information contained in this manual may be updated from time-to-time due to product improvements, etc., and may not conform in every respect to former issues.

To report errors or inconsistencies, call or email:

#### Delta Tau Data Systems, Inc. Technical Support

Phone: +1 (818) 717-5656

Fax: +1 (818) 998-7807

Email: <a href="mailto:support@deltatau.com">support@deltatau.com</a>

Web: <a href="mailto:www.deltatau.com">www.deltatau.com</a>

## **Operating Conditions**

All Delta Tau Data Systems, Inc. motion controller, accessory, and amplifier products contain static sensitive components that can be damaged by incorrect handling. When installing or handling Delta Tau Data Systems, Inc. products, avoid contact with highly insulated materials. Only qualified personnel should be allowed to handle this equipment.

In the case of industrial applications, we expect our products to be protected from hazardous or conductive materials and/or environments that could cause harm to the controller by damaging components or causing electrical shorts. When our products are used in an industrial environment, install them into an industrial electrical cabinet to protect them from excessive or corrosive moisture, abnormal ambient temperatures, and conductive materials. If Delta Tau Data Systems, Inc. products are directly exposed to hazardous or conductive materials and/or environments, we cannot guarantee their operation.

### **Safety Instructions**

Qualified personnel must transport, assemble, install, and maintain this equipment. Properly qualified personnel are persons who are familiar with the transport, assembly, installation, and operation of equipment. The qualified personnel must know and observe the following standards and regulations:

IEC364resp.CENELEC HD 384 or DIN VDE 0100

IEC report 664 or DIN VDE 0110

National regulations for safety and accident prevention or VBG 4

Incorrect handling of products can result in injury and damage to persons and machinery. Strictly adhere to the installation instructions. Electrical safety is provided through a low-resistance earth connection. It is vital to ensure that all system components are connected to earth ground.

This product contains components that are sensitive to static electricity and can be damaged by incorrect handling. Avoid contact with high insulating materials (artificial fabrics, plastic film, etc.). Place the product on a conductive surface. Discharge any possible static electricity build-up by touching an unpainted, metal, grounded surface before touching the equipment.

Keep all covers and cabinet doors shut during operation. Be aware that during operation, the product has electrically charged components and hot surfaces. Control and power cables can carry a high voltage, even when the motor is not rotating. Never disconnect or connect the product while the power source is energized to avoid electric arcing.

Warning

A Warning identifies hazards that could result in personal injury or death. It precedes the discussion of interest.

**Caution**

A Caution identifies hazards that could result in equipment damage. It precedes the discussion of interest.

A Note identifies information critical to the understanding or use of the equipment. It follows the discussion of interest.

| REVISION HISTORY |                                                |          |    |    |  |  |  |  |

|------------------|------------------------------------------------|----------|----|----|--|--|--|--|

| REV.             | REV. DESCRIPTION DATE CH                       |          |    |    |  |  |  |  |

| 1                | Added CE declaration                           | 06/07/06 | CP | SF |  |  |  |  |

| 2                | Added UL Approval and agency safety info.      | 09/30/09 | CP | SF |  |  |  |  |

| 3                | Corrected BEQU2 Error                          | 02/04/10 | CP | SF |  |  |  |  |

| 4                | Updated connection diagram, general formatting | 07/21/15 | CP | RN |  |  |  |  |

|                  |                                                |          |    |    |  |  |  |  |

|                  |                                                |          |    |    |  |  |  |  |

|                  |                                                |          |    |    |  |  |  |  |

|                  |                                                |          |    |    |  |  |  |  |

This page intentionally left blank

#### **Table Of Contents**

| INTRODUCTION                                                    | 9  |

|-----------------------------------------------------------------|----|

| Overview                                                        | 9  |

| Features                                                        | 9  |

| Board Configuration                                             | 10 |

| SPECIFICATIONS                                                  | 11 |

| Environmental Specifications                                    | 11 |

| Physical Specifications                                         | 11 |

| Electrical Specifications                                       | 12 |

| Agency Approval and Safety                                      | 12 |

| HARDWARE SETUP                                                  | 13 |

| Switch Configuration                                            | 13 |

| UMAC Address DIP Switch S1                                      | 13 |

| Legacy MACRO Dip Switch Settings                                | 13 |

| Converting Memory Address from Turbo to Power PMAC              | 14 |

| ACC-24E2 Clock Settings                                         | 14 |

| Resistor Pack Configuration                                     | 15 |

| Differential/Single-Ended and Encoder Loss Detection            |    |

| Termination Resistors Packs                                     |    |

| Limit/Flag Voltage Level Resistor Packs                         |    |

| UBUS Specific Resistor Packs                                    |    |

| UBUS Specific Resistor Packs  OPTO-Isolation Considerations     |    |

|                                                                 |    |

| ACC-24E2 Limit and Flag Wiring                                  |    |

| Connecting Limits/Flags to the ACC-24E2 Amplifier Fault Circuit |    |

| •                                                               |    |

| Amplifier Enable Circuit                                        |    |

| ACC-24E2A Encoder Loss Detection with UMAC Turbo CPU            |    |

| ACC-24E2A Encoder Loss Detection with UMAC MACRO CPU            |    |

| ACC-24E2A Encoder Loss Detection with Power PMAC CPU            |    |

| Position Compare Port Driver IC                                 |    |

| CONNECTIONS                                                     | 23 |

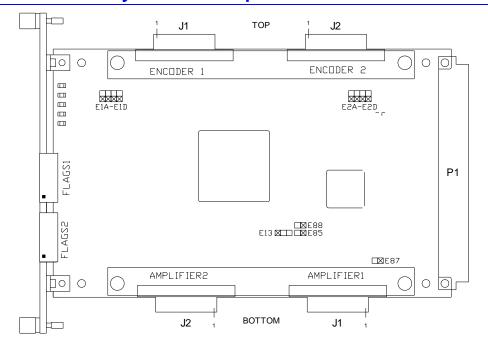

| ACC-24E2A Board Layout - Terminal Block Option                  |    |

| ACC-24E2A Board Layout - DB15 Option                            |    |

| Mating Connectors                                               |    |

| Terminal Block Connectors                                       |    |

| DB15 Connector Option                                           | 24 |

| Indicators                                             | 24 |

|--------------------------------------------------------|----|

| Overall Wiring Diagram                                 | 25 |

| Sample Wiring Diagrams                                 | 26 |

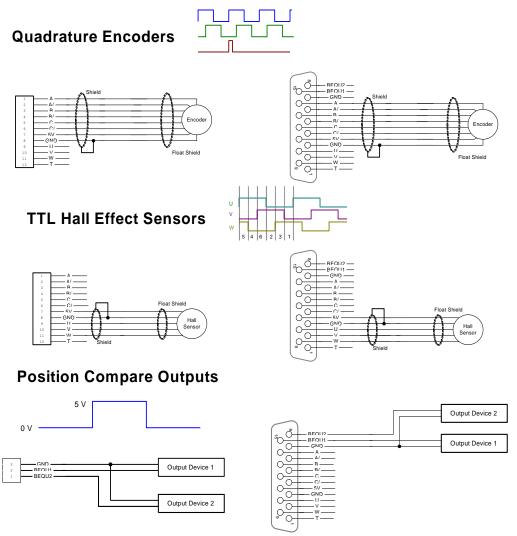

| TTL Level Inputs and Outputs                           | 26 |

| Position Limits, Home Flag, and User Flag              | 27 |

| DAC Outputs                                            |    |

| Stepper Drive, Pulse and Direction Outputs (TTL Level) |    |

| Amplifier Fault Inputs                                 |    |

| Amplifier Enable Outputs                               | 30 |

| SOFTWARE SETUP                                         |    |

| Using ACC-24E2A with UMAC Turbo                        | 31 |

| Servo IC Numbering                                     | 31 |

| Servo Channel Numbering                                | 31 |

| Multi-Channel I-Variables                              |    |

| Single-Channel I-Variables                             |    |

| Encoder Conversion Table I-Variables                   |    |

| Motor Addressing I-Variables                           |    |

| TURBO UMAC Example Setups                              |    |

| Using ACC-24E2A with ULTRALITE/MACRO STATION           |    |

| Clocks and Strobe Word                                 |    |

| Node-Specific Gate Array MI-Variables                  |    |

| Using ACC-24E2A with Power PMAC                        |    |

| DSPGATE1 Servo IC Data Structure Elements              |    |

| Software Setup for Clock Signals                       |    |

| Software Setup for Position Feedback                   |    |

| MLDT Sensors                                           |    |

| Software Setup for Flags                               |    |

| Software Setup for Amplifiers                          |    |

| DSPGATE1 (PMAC2-Style Servo ASIC) Register Elements    |    |

| Using ACC-24E2A for MLDT Feedback                      |    |

| MLDT Hardware Setup of the ACC-24E2A                   |    |

| MLDT Software Setup of the UMAC Turbo                  |    |

| MLDT Feedback for UMAC-MACRO                           |    |

| ACC-24E2A TERMINAL BLOCK DESCRIPTION                   | 68 |

| Connector TB1 TOP - Encoder 1                          | 68 |

| Connector TB2 Top - Encoder 2                          |    |

| Connector TB3 Top – EQU Outputs                        |    |

| Connector TB1 Bottom Amp – Out 1                       |    |

| Connector TB2 Bottom Amp – Out 2                       |    |

| Connector TB3 Bottom – Analog Power                    |    |

| Connector 1 D J Dottom Allaiog 1 0 wel                 |    |

| Connector TB1 Front- Limits 1                           | 71 |

|---------------------------------------------------------|----|

| Connector TB2 Front- Limits 2                           | 71 |

| ACC-24E2 OPTION 1A TERMINAL BLOCK DESCRIPTION           | 72 |

| Connector TB1 Top - Encoder 3                           | 72 |

| Connector TB2 Top – Encoder 4                           | 72 |

| Connector TB3 Top – EQU Outputs                         | 73 |

| Connector TB1 Bottom Amp-Out 3                          | 74 |

| Connector TB2 Bottom Amp-Out 4                          | 74 |

| Connector TB3 Bottom-Analog Power                       | 74 |

| Connector TB1 Front - Limits 3                          | 75 |

| Connector TB2 Front - Limits 4                          | 75 |

| ACC-24E2A DB15 CONNECTOR OPTION                         | 76 |

| DB15 Style Connector J1 Top - Encoder 1 / EQU           | 76 |

| DB15 Style Connector J2 Top - Encoder 2 / EQU           | 76 |

| DB15 Style Connector J1 Bottom Amp – Out 1/Analog Power | 78 |

| DB15 Style Connector J2 Bottom Amp – Out 2/Analog Power | 78 |

| Connector TB1 Front-Limits 1                            | 79 |

| Connector TB2 Front-Limits 2                            | 79 |

| UBUS PINOUTS                                            | 80 |

| P1 UBUS (96-Pin Header)                                 |    |

| DECLARATION OF CONFORMITY                               | 81 |

| E-POINT JUMPER SETTINGS                                 | 82 |

| ACC-24E2A Base Board (Channels* 1 and 2)                | 82 |

| ACC-24E2A Option 1 Board (Channels 3 and 4)             | 83 |

Table Of Contents viii

### INTRODUCTION

#### **Overview**

The ACC-24E2A is an axis expansion board which provides 2 or 4 channels of PMAC2-style servo interface circuitry for UMAC and Ultralite/MACRO Station controllers. The ACC-24E2A is part of the UMAC or MACRO Pack family of expansion cards and these accessory cards are designed to plug into an industrial 3U rack system.

Many ACC-24E2A features are common to other accessories of the ACC-24E2 family; these common features are referred to in this manual as ACC-24E2x.

Up to eight ACC-24E2A boards can be connected to one UMAC providing up to 32 additional channels of servo interface circuitry. The 16-Axes MACRO CPU can support four ACC-24E2x cards and the 8-Axes MACRO CPU can support 2 ACC-24E2x.

The ACC-24E2x board contains no processor; it has one highly integrated 4-channel PMAC2-style Servo IC with the buffering circuitry and connectors around them. The two-axis ACC-24E2x plugs into the backplane and uses one slot in the rack. If two more axes are needed, ACC-24E2x Option 1 can be plugged into the ACC-24E2x connectors. The ACC-24E2x with its Option 1 card takes up a total of two slots.

Some new features added to the family of ACC-24E2x breakout boards include:

Loss of encoder circuit

5V to 24V Flag inputs

Pulse and direction outputs for stepper systems or MLDTs

#### **Features**

The ACC-24E2A board can be used with any UMAC or MACRO Station CPU, interfacing through the expansion port.

The ACC-24E2A supports a wide variety of servo and stepper interfaces:

Analog +/-10V velocity commands

Analog +/-10V torque commands

Sinusoidal analog +/-10V phase current commands

Pulse-and-direction commands

Introduction 9

### **Board Configuration**

An ACC-24E2A comes standard with one Servo IC providing four servo interface channels, which are brought out on terminal blocks (standard) or DB15 connector. Each channel of servo interface circuitry includes the following:

- Two output command signal sets, configurable as either:

- One pulse-and-direction

- Two DAC outputs

- 3-channel differential/single-ended encoder input

- Eight input flags, two output flags

**Option 1A:** If Option 1A is ordered, the circuitry and input/output connectors are provided for the third and fourth channels associated with the Servo IC on the main ACC-24E2A. The command signals for this option are  $\pm 10$ V.

**Option 1D:** If Option 1D is ordered, the circuitry and input/output connectors are provided for the third and fourth channels associated with the Servo IC on the main ACC-24E2A. The command signals for this option are digital PWM signals for direct PWM commutation. The option 1D description can be found in the ACC-24E2 manual.

**Option DB:** If the option DB is ordered the outputs and inputs to the amplifiers and encoders will be serviced from DB15 connectors. See ACC-24E2A DB15 Connector Option section for pin outs.

Introduction 10

## **SPECIFICATIONS**

## **Environmental Specifications**

| Description           | Specification              |

|-----------------------|----------------------------|

| Operating Temperature | 0°C to 45°C,               |

| Storage Temperature   | -25°C to 70°C              |

| Humidity              | 10% to 95 % non-condensing |

## **Physical Specifications**

| Description                                                                                     | Specification                                                                       | Notes                                            |  |  |  |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|--|

| Dimensions w/o Option 1A                                                                        | Length: 16.256 cm (6.4 in.)<br>Height: 10 cm (3.94 in.)<br>Width: 2.03 cm (0.8 in.) |                                                  |  |  |  |  |

| Dimensions with Option 1A                                                                       | Length: 16.256 cm (6.4 in.)<br>Height: 10 cm (3.94 in.)<br>Width: 4.06 cm (1.6 in.) |                                                  |  |  |  |  |

| Weight w/o Option 1A                                                                            | 192 g                                                                               | Front Plate included                             |  |  |  |  |

| Weight with Option 1A                                                                           | 370 g                                                                               | Front Plate included                             |  |  |  |  |

| Terminal Block Connectors                                                                       | FRONT-MC1,5/12-ST3,81<br>FRONT-MC1,5/5-ST3,81<br>FRONT-MC1,5/3-ST3,81               | Terminal Blocks from Phoenix<br>Contact. UL-94V0 |  |  |  |  |

| DB Option Connectors                                                                            | DB15 Female                                                                         | UL-94V0                                          |  |  |  |  |

| The width is the width of the front plate. The length and height are the dimensions of the PCB. |                                                                                     |                                                  |  |  |  |  |

Specifications 11

## **Electrical Specifications**

| Description                                 | Specification                                                   |

|---------------------------------------------|-----------------------------------------------------------------|

| ACC-24E2A Power Requirements                | 5V @ 0.55A (±10%)<br>+15V @ 0.16A (±10%)<br>-15V @ 0.07A (±10%) |

| ACC-24E2A with Option 1A Power Requirements | 5V @ 0.95A (±10%)<br>+15V @ 0.30A (±10%)<br>-15V @ 0.12A (±10%) |

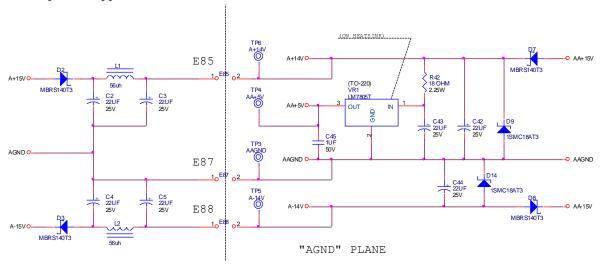

If more than four ACC-24E2A's with Option 1A are used in a UMAC system, the ACC-E1 or ACC-F1 power supplies will not have enough 15V power. Delta Tau recommends using an external ±15V power supply for systems with more than four ACC-24E2A boards. The external power supply should be connected to the unit from the terminal blocks (TB3 bottom) or DB connections (J1 or J2 Bottom) and jumpers E85, E87, and E88 must also be removed.

## **Agency Approval and Safety**

| Item               | Description                                                                                                                               |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| CE Mark            | Full Compliance                                                                                                                           |  |

| EMC                | EN55011 Class A Group 1<br>EN61000-3-2 Class A<br>EN61000-4-2<br>EN61000-4-3<br>EN61000-4-4<br>EN61000-4-5<br>EN61000-4-6<br>EN61000-4-11 |  |

| Safety             | EN 61010-1                                                                                                                                |  |

| UL                 | UL 61010-1 File E314517                                                                                                                   |  |

| cUL                | CAN/CSA C22.2 No. 1010.1-92 File E314517                                                                                                  |  |

| Flammability Class | UL 94V-0                                                                                                                                  |  |

Specifications 12

## **HARDWARE SETUP**

## **Switch Configuration**

### **UMAC Address DIP Switch S1**

| Ch:    |                   | Base Ad | dress    |           |     | SW1 Positions |     |     |     |     |

|--------|-------------------|---------|----------|-----------|-----|---------------|-----|-----|-----|-----|

| Chip   | TURBO             | MACRO   | POWER    |           | 6   | 5             | 4   | 3   | 2   | 1   |

| Select | TURBU             | MACRO   | Offset   | Index (n) | U   | 3             | 4   | 3   | 2   | 1   |

|        | \$78200           | \$8000  | \$600000 | 4         | ON  | ON            | ON  | ON  | ON  | ON  |

|        | \$78220           | N/A     | \$600100 | 5         | ON  | ON            | ON  | ON  | OFF | ON  |

| CS10   | \$78300           | \$8040  | \$700000 | 6         | ON  | ON            | ON  | ON  | ON  | OFF |

|        | \$78320           | N/A     | \$700100 | 7         | ON  | ON            | ON  | ON  | OFF | OFF |

|        |                   |         | 1        | ·         | 1   | 1             |     | ı   | ı   |     |

|        | \$79200           | \$9000  | \$608000 | 8         | ON  | ON            | ON  | OFF | ON  | ON  |

| CC12   | \$79220           | N/A     | \$608100 | 9         | ON  | ON            | ON  | OFF | OFF | ON  |

| CS12   | \$79300           | \$9040  | \$708000 | 10        | ON  | ON            | ON  | OFF | ON  | OFF |

|        | \$79320           | N/A     | \$708100 | 11        | ON  | ON            | ON  | OFF | OFF | OFF |

|        | Φ <b>7.4.2</b> 00 | Φ 4 000 | фc10000  | 10        | ONI | ON            | OFF | ON  | ON  | ON  |

|        | \$7A200           | \$A000  | \$610000 | 12        | ON  | ON            | OFF | ON  | ON  | ON  |

| CS14   | \$7A220           | N/A     | \$610100 | 13        | ON  | ON            | OFF | ON  | OFF | ON  |

| CDIT   | \$7A300           | \$A040  | \$710000 | 14        | ON  | ON            | OFF | ON  | ON  | OFF |

|        | \$7A320           | N/A     | \$710100 | 15        | ON  | ON            | OFF | ON  | OFF | OFF |

|        | \$7B200           | \$B000  | \$618000 | 16        | ON  | ON            | OFF | OFF | ON  | ON  |

| GG16   | \$7B220           | N/A     | \$618100 | 17        | ON  | ON            | OFF | OFF | OFF | ON  |

| CS16   | \$7B300           | \$B040  | \$718000 | 18        | ON  | ON            | OFF | OFF | ON  | OFF |

|        | \$7B320           | N/A     | \$718100 | 19        | ON  | ON            | OFF | OFF | OFF | OFF |

- ON designates Closed. OFF designates Open

- Factory default is all ON

### **Legacy MACRO Dip Switch Settings**

| S1-1                                                                                   | S1-2* | S1-3 | S1-4 | Board No. | IC No. | Base Address |  |

|----------------------------------------------------------------------------------------|-------|------|------|-----------|--------|--------------|--|

| ON                                                                                     | ON    | OFF  | OFF  | 1         | 2      | \$00C040     |  |

| OFF                                                                                    | OFF   | OFF  | OFF  | 2         | 3      | \$00C060     |  |

| * Always set to OFF for legacy MACRO Stations (part number 602804-100 thru 602804-104) |       |      |      |           |        |              |  |

S1-5 and S1-6 are used to determine whether the ACC-24E2 is communicating to a Turbo 3U PMAC or a MACRO Station CPU.

| S1-5 S1-6 |     | Function             |

|-----------|-----|----------------------|

| OFF       | OFF | 3U MACRO Station use |

### **Converting Memory Address from Turbo to Power PMAC**

To convert a Turbo PMAC Y memory address to Power PMAC corresponding address the following formula can be used:

$$A_{PT} = V_0 + A_{PB} \tag{1}$$

Where  $A_{PT}$  is the target Power PMAC memory address.  $A_{PB}$  is the Power PMAC base address and  $V_O$  is the memory offset given by:

$$V_O = (\text{int}) \left[ \frac{A_{TT} - A_{TB}}{8} \right] \times 64 + ((A_{TT} - A_{TB}) \% 8) \times 4$$

(2)

Where  $A_{TB}$  is the UMAC Turbo base address of the card, and  $A_{TT}$  is the address of the UMAC Turbo target memory location. Note that (int) in Equation 2 indicates that expression within the square brackets following it must be cast to an integer before use. If the expression valuates to a non-integer, the fractional part must be truncated, not rounded. The "%" sign indicates that modulo operator; e.g, a%b will yield the remainder from the quotient a/b.

If converting X memory address this formula can be used:

$$A_{PT} = V_0 + A_{PB} + 32 \tag{3}$$

### **ACC-24E2 Clock Settings**

The Phase Clock and Servo Clock must be configured on each ACC-24E2A baseboard. Each system can have only one source for the servo and phase clocks and jumpers must be set appropriately to avoid a timing conflict or a watchdog condition.

Starting in UMAC Turbo firmware version 1.937, the firmware will set the clock settings for the ACC-24E2 cards in the UBUS automatically. To enable this feature, set jumper E13 from 2 to 3 for all of the ACC-24E2s plugged into the UMAC system. At re-initialization (either \$\$\$\*\*\* command or power up with E3 jumpered on UMAC), the firmware will know that all of the cards are in the auto configuration setup and will assign the card with the lowest base address setting (usually \$78200) the task of sourcing the clocks by setting variable I19 to the appropriate register. The clocks will be set initially to the factory default servo update cycle and phase clock cycle. For a better understanding of this feature, refer to description of I19 in the Turbo Software Reference Manual.

For UMAC Turbo systems with firmware older than version 1.937, set one of the ACC-24E2s to transmit (E13 set 2-3) the phase and servo clock (usually the card at the lowest base address setting) and set the rest of the ACC-24E2s to receive (E13 set 1-2) the phase and servo clocks.

For MACRO systems, the clock select jumper should be set to receive servo and phase clocks because the MACRO CPU always provides the clocks. For the ACC-24E2A, E13 should be set 1-2.

### **Resistor Pack Configuration**

#### **Differential/Single-Ended and Encoder Loss Detection**

The differential input signal pairs to the PMAC have user-configurable pull-up/pull-down resistor networks to permit the acceptance of either single-ended or differential signals in one setting, or the detection of lost differential signals in another setting.

- The '+' inputs of each differential pair each have a hard-wired 1 k $\Omega$  pull-up resistor to +5V. This cannot be changed.

- The '-' inputs of each differential pair each have a hard-wired 2.2 k $\Omega$  resistor to +5V; also each has another 2.2 k $\Omega$  resistor as part of a socketed resistor pack that can be configured as a pull-up resistor to +5V, or a pull-down resistor to GND.

If this socketed resistor is configured as a pull-down resistor (the default configuration), the combination of pull-up and pull-down resistors on this line acts as a voltage divider, holding the line at +2.5V in the absence of an external signal. This configuration is required for single-ended inputs using the '+' lines alone; it is desirable for unconnected inputs to prevent the pick-up of spurious noise; it is permissible for differential line-driver inputs.

If this socketed resistor is configured as a pull-up resistor (by reversing the SIP pack in the socket), the two parallel  $2.2 \text{ k}\Omega$  resistors act as a single  $1.1 \text{ k}\Omega$  pull-up resistor, holding the line at +5V in the absence of an external signal. This configuration is required if encoder-loss detection is desired; it is required if complementary open-collector drivers are used; it is permissible for differential line-driver inputs even without encoder loss detection.

If Pin 1 of the resistor pack (marked by a dot on the pack) matches Pin 1 of the socket (marked by a wide white square solder pin on the front side of the board), then the pack is configured as a bank of pull-down resistors. If the pack is reversed in the socket, it is configured as a bank of pull-up resistors.

The following table lists the pull-up/pull-down resistor pack for each input device:

| Device    | Resistor Pack | Pack Size | SIP    |

|-----------|---------------|-----------|--------|

| Encoder 1 | RP22          | 6-pin     | 2.2 ΚΩ |

| Encoder 2 | RP24          | 6-pin     | 2.2 ΚΩ |

| Encoder 3 | RP22          | 6-pin     | 2.2 ΚΩ |

| Encoder 4 | RP24          | 6-pin     | 2.2 ΚΩ |

#### **Termination Resistors Packs**

The ACC-24E2A provides sockets for termination resistors on differential input pairs coming into the board. As shipped, there are no resistor packs in these sockets. If these signals are brought long distances into the ACC-24E2A board and ringing at signal transitions is a problem, SIP resistor packs may be mounted in these sockets to reduce or eliminate the ringing.

All termination resistor packs have independent resistors (no common connection) with each resistor using two adjacent pins as shown below.

#### Isolated Resistor Network

| Channel 1 | Channel 2 | SIP         | Description                                                        |

|-----------|-----------|-------------|--------------------------------------------------------------------|

| RP23      | RP25      | $220\Omega$ | Termination resistor to reduce ringing (not installed by default). |

#### **Limit/Flag Voltage Level Resistor Packs**

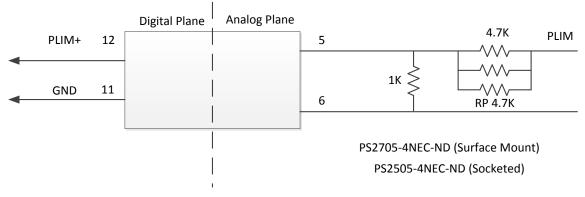

The ACC-24E2A limit and flag circuits also give the flexibility to wire in standard 12V to 24V limits and flags or wire in 5V level limits and flags on a channel basis. The default is set for the standard 12V to 24V inputs but if the resistor pack is added to the circuit, the card can read 5V inputs. Channel Specific Resistor Packs

| Channel 1 | Channel 2 | SIP | Description           |

|-----------|-----------|-----|-----------------------|

| RP45      | RP46      | 1ΚΩ | Install for 5V limits |

## **UBUS Specific Resistor Packs**

| Resistor Pack | SIP Description |                                                              |

|---------------|-----------------|--------------------------------------------------------------|

| RP5           | $220\Omega$     | Terminator (not installed, only used for non-UBUS)           |

| RP6           | 2.2ΚΩ           | Pull Down for old MACRO CPU Pull Up for UMAC Turbo and MACRO |

### **UBUS Specific Resistor Packs**

| Resistor Pack | SIP | Description                               |

|---------------|-----|-------------------------------------------|

| RP7           |     | Installed by default, Phase/Servo signals |

### **OPTO-Isolation Considerations**

As shipped from the factory, the ACC-24E2A obtains its power from the UMAC Backplane or UBUS. Using this type of setup will defeat opto isolation since the analog ground plane will be tied directly to the digital ground plane.

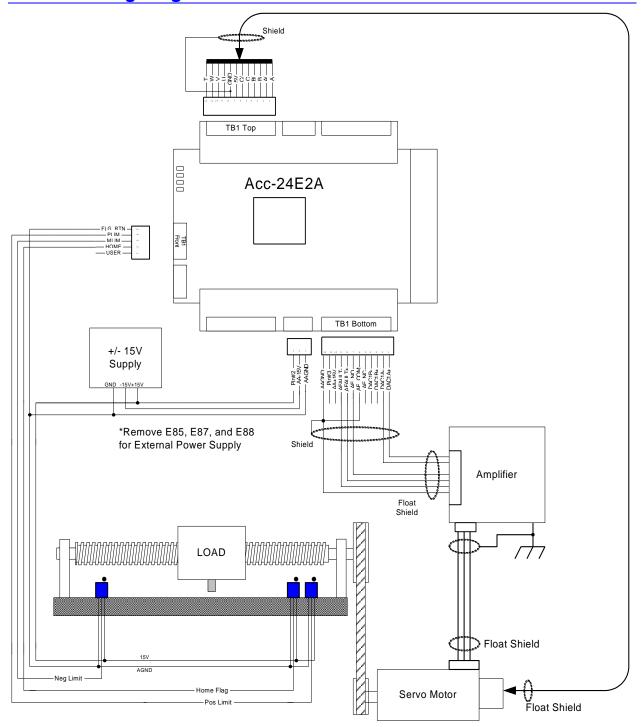

To optically isolate the analog ground plane from the digital ground plane, connect an external power supply to one of the many AA+15V, AA-15V, and AAGND inputs on the ACC-24E2A terminal blocks or DB connectors. Also, remove the E85, E87, and E88 jumpers to isolate the external power from the UBUS power supplies.

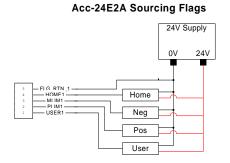

## **ACC-24E2 Limit and Flag Wiring**

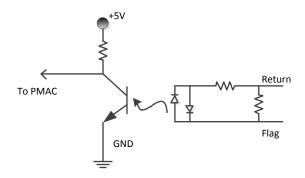

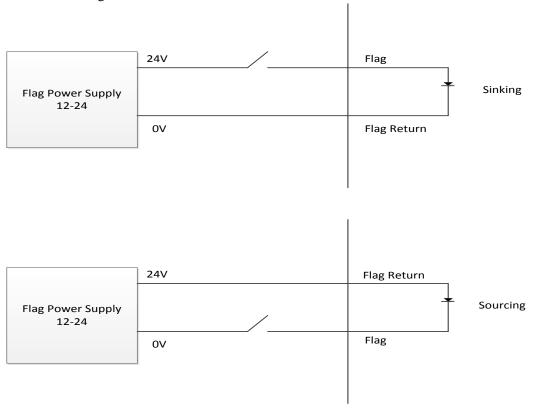

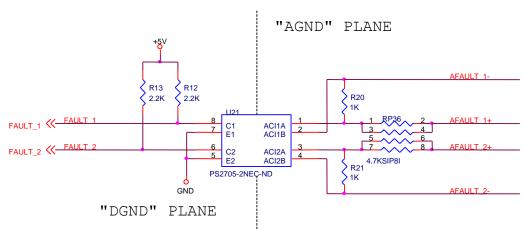

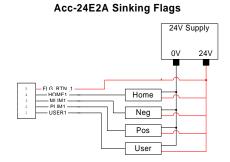

The ACC-24E2 allows the use of sinking or sourcing position limits and flags to the controller. The opto-isolator IC used is a PS2705-4NEC-ND quad photo-transistor output type. This IC allows the current to flow from return to flag (sourcing) or from flag to return (sinking).

A sample of the positive limit circuit is shown below. The 4.7K resistor packs used will allow 12-24V flag inputs. If 0-5V flags are used, then a  $1K\Omega$  resistor pack (RP) can be placed in either RP45 or RP46 (refer to the Resistor Pack Configuration section of this manual). If these resistor packs are not added, all flags ( $\pm$ Limits, Home, User, and amplifier fault) will be referenced from 0-5V.

## **Connecting Limits/Flags to the ACC-24E2**

The following diagram illustrates the sinking and sourcing connections to an ACC-24E2. This example uses 12-24V flags.

### **Amplifier Fault Circuit**

The amplifier fault circuit for the ACC-24E2A is functionally the same circuit as the limits and flag circuit.

For single-ended amplifier fault inputs, typically the AFAULT+ would be the actual signal input from the amplifier and the AFAULT- can be considered the reference.

#### **Single Ended Amplifier Fault Inputs**

| Amplifier<br>Fault Signal | Ixx24 (Bit 23) | Fault+               | Fault-                                     | Fail Safe |

|---------------------------|----------------|----------------------|--------------------------------------------|-----------|

| Low True                  | (Recommended)  | Tied to Fault Signal | Tied to Reference (GND) of Fault Signal    | Yes       |

|                           | 0              | Tied To Fault Signal | Tied to +V                                 | No        |

|                           | 1              | Tied To Fault Signal | Tied to +V                                 | No        |

| High True                 | (Recommended)  | Tied To Fault Signal | Tied to Reference<br>(GND) of Fault Signal | No        |

Mxx23 (Amplifier Fault Bit) is set to 0 if current is conducting from Fault+ to Fault- or vice versa and is set to 1 if current is not conducting.

- Low True Amplifier indicates that the fault signal is low, if amplifier fault triggers.

- High True Amplifier indicates that the fault signal is high, if amplifier fault triggers.

- Factory default is all

- Non recommended Ixx24s do not work with amplifiers that their low signal is an open circuit.

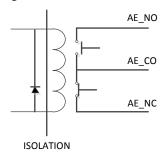

### **Amplifier Enable Circuit**

Most amplifiers have an enable/disable input that permit s complete shutdown of the amplifier regardless of the voltage of the command signal. The ACC-24E2A AENA line is meant for this purpose. The amplifier enable signals of the ACC-24E2A is controlled by a relay with normal opened and normal closed dry contacts as shown in the diagram below:

#### **Loss of Encoder Circuit**

The encoder-loss detection circuitry works for differential incremental encoders only. In proper operation, the digital states of the complementary inputs for a channel (e.g. A and A/) always should be opposite: when one is high, the other is low. If for some reason, such as a cable connection coming undone, one or more of the signal lines is no longer driven, pull-up resistors on the input line pull and hold the signal high. The encoder-loss detection circuitry uses exclusive-or (XOR) gates on each complementary pair to detect whether the signals are in the same or opposite states. These results are combined to produce a single encoder-loss status bit that the processor can read.

This technique requires that both signal lines of the pair have pull-up resistors. Note that this is not the default configuration of a PMAC as it is shipped. The complementary lines (A/ and B/) are pulled to 2.5V in a voltage-divider configuration as shipped to be able to accept both single-ended and normal differential inputs. This must be changed to a pull-up configuration which involves reversing a socketed resistor pack on the ACC-24E2A.

#### ACC-24E2A Encoder Loss Detection with UMAC Turbo CPU

| Channel | Resistor<br>Pack | Status Bit Address (Even-<br>Numbered Servo IC)* | Status Bit Address (Odd-<br>Numbered Servo IC)* | Status Bit<br>Name | Bit Error<br>State |

|---------|------------------|--------------------------------------------------|-------------------------------------------------|--------------------|--------------------|

| 1       | RP22             | Y:\$07xF08,5                                     | Y:\$07xF0C,5                                    | QL_1-              | 0                  |

| 2       | RP24             | Y:\$07xF09,5                                     | Y:\$07xF0D,5                                    | QL_2-              | 0                  |

| 3       | RP22**           | Y:\$07xF0A,5                                     | Y:\$07xF0E,5                                    | QL_3-              | 0                  |

| 4       | RP24**           | Y:\$07xF0B,5                                     | Y:\$07xF0F,5                                    | QL_4-              | 0                  |

- The x digit in this hex address matches the value (8, 9, A, or B) in the fourth digit from the right in the board's own base address (e.g. \$079200). If alternate addressing of Servo ICs is used (e.g. Servo IC 2\*), add \$20 to these addresses.

- These resistor packs are on the Option 1A piggyback board (if present) of the module, not on the baseboard.

#### ACC-24E2A Encoder Loss Detection with UMAC MACRO CPU

| Channel | Resistor<br>Pack | Status Bit Address (First-<br>Servo IC)* | Status Bit Address<br>(Second Servo IC)* | Status Bit "Name" | Bit Error<br>State |

|---------|------------------|------------------------------------------|------------------------------------------|-------------------|--------------------|

| 1       | RP22             | Y:\$B8C8,5                               | Y:\$B8EC,5                               | QL_1-             | 0                  |

| 2       | RP24             | Y:\$B8C9,5                               | Y:\$B8ED,5                               | QL_2-             | 0                  |

| 3       | RP22             | Y:\$B8CA,5                               | Y:\$B8EE,5                               | QL_3-             | 0                  |

| 4       | RP24             | Y:\$B8CB,5                               | Y:\$B8EF,5                               | QL_4-             | 0                  |

- First Servo IC has base address \$C040; second Servo IC has base address \$C060.

- These resistor packs are on the Option 1A piggyback board (if present) of the module, not on the baseboard.

#### ACC-24E2A Encoder Loss Detection with Power PMAC CPU

| Channel | Resistor<br>Pack | Status Bit Address (Even-<br>Numbered Servo IC)* | Status Bit Address (Odd-<br>Numbered Servo IC)* | Status Bit<br>Name | Bit Error<br>State |

|---------|------------------|--------------------------------------------------|-------------------------------------------------|--------------------|--------------------|

| 1       | RP22             | u.io:\$Dxx040.13.1                               | u.io:\$Dxx050.13.1                              | QL_1-              | 0                  |

| 2       | RP24             | u.io:\$Dxx044.13.1                               | u.io:\$Dxx054.13.1                              | QL_2-              | 0                  |

| 3       | RP22             | u.io:\$Dxx048.13.1                               | u.io:\$Dxx058.13.1                              | QL_3-              | 0                  |

| 4       | RP24             | u.io:\$Dxx04C.13.1                               | u.io:\$Dxx05C.13.1                              | QL_4-              | 0                  |

- The xx digit in this hex address matches the value (00, 08, 10, or 18) in the fourth and fifth digits from the right in the board's own base address (e.g. \$608000). If alternate addressing of Servo ICs is used (e.g. Servo IC 2\*), add \$100 to these addresses.

- These resistor packs are on the Option 1A piggyback board (if present) of the module, not on the baseboard.

## **Position Compare Port Driver IC**

As with the other PMAC controllers, the UMAC has the high-speed position compare outputs allowing the firing of an output based on position. This circuit will fire within 100 nsec of reaching the desired position. The position compare output port on ACC-24E2x has driver IC at component U27. The following table lists the properties of each driver IC:

| Part     | # of Pins | Max Voltage and Current | Output Type | Max Frequency |

|----------|-----------|-------------------------|-------------|---------------|

| DS75451N | 8         | 5V, 10 mA               | Totem-Pole  | 5 MHz         |

## **CONNECTIONS**

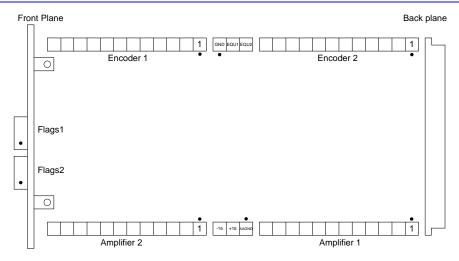

## **ACC-24E2A Board Layout - Terminal Block Option**

## **ACC-24E2A Board Layout - DB15 Option**

## **Mating Connectors**

## **Terminal Block Connectors**

| Name        | Manufacturer    | Pins | Туре                  | Details               |

|-------------|-----------------|------|-----------------------|-----------------------|

| TB1- Top    | Phoenix Contact | 12   | FRONT-MC1,5/12-ST3,81 | Encoder 1 Inputs      |

| TB2- Top    | Phoenix Contact | 12   | FRONT-MC1,5/12-ST3,81 | Encoder 2 Inputs      |

| TB3- Top    | Phoenix Contact | 3    | FRONT-MC1,5/3-ST3,81  | Compare Outputs       |

| TB1- Bottom | Phoenix Contact | 12   | FRONT-MC1,5/12-ST3,81 | Amplifier 1 Outputs   |

| TB2- Bottom | Phoenix Contact | 12   | FRONT-MC1,5/12-ST3,81 | Amplifier 2 Outputs   |

| TB3- Bottom | Phoenix Contact | 3    | FRONT-MC1,5/3-ST3,81  | External Power Inputs |

| TB1- Front  | Phoenix Contact | 5    | FRONT-MC1,5/5-ST3,81  | Channel 1 Flags       |

| TB2 Front   | Phoenix Contact | 5    | FRONT-MC1,5/5-ST3,81  | Channel 2 Flags       |

## **DB15 Connector Option**

| Name       | Manufacturer | Pins | Туре         | Details                                     |

|------------|--------------|------|--------------|---------------------------------------------|

| J1- Top    | AMP          | 15   | AMP 745072-2 | Encoder 1 Inputs and Compare Outputs        |

| J2- Top    | AMP          | 15   | AMP 745072-2 | Encoder 2 Inputs and Compare Outputs        |

| J1- Bottom | AMP          | 15   | AMP 745072-2 | Amplifier 1 Outputs and Analog Power Inputs |

| J2- Bottom | AMP          | 15   | AMP 745072-2 | Amplifier 2 Outputs and Analog Power Inputs |

## **Indicators**

| LED | Color | Description         |

|-----|-------|---------------------|

| D5  | Amber | Amplifier 1 Enabled |

| D6  | Amber | Amplifier 2 enabled |

| D10 | Green | Encoder 1 Power OK  |

| D11 | Green | Encoder 2 Power OK  |

| D17 | Green | Analog Power Good   |

## **Overall Wiring Diagram**

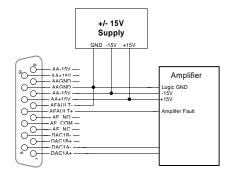

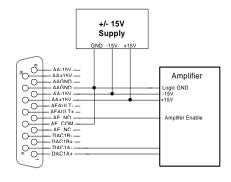

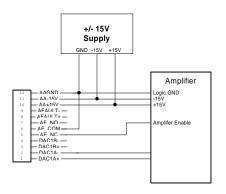

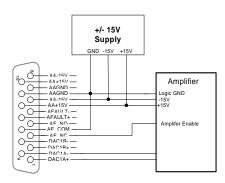

This is a general example of a system with sourcing flags and normally open amplifier enable output from the Acc-24E2A. For opto-isolation an external power supply is used and E85, E87, and E88 have been removed from the Acc-24E2A.

## **Sample Wiring Diagrams**

This section has typical wiring diagrams for the TTL level inputs, flags and limits, DAC and PFM outputs, amplifier enable, and amplifier fault.

## **TTL Level Inputs and Outputs**

### Position Limits, Home Flag, and User Flag

#### sition Ellints, frome fridg, and osci fri

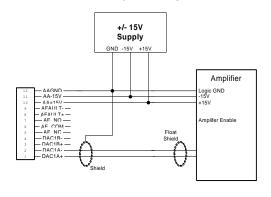

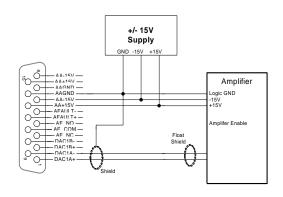

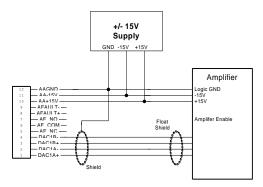

## **DAC Outputs**

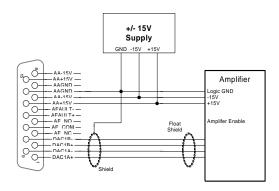

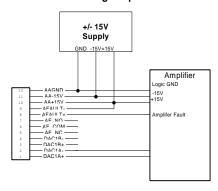

Sample diagrams shown below utilize a separate  $\pm 15V$  power supply for opto-isolation. E85, E87, and E88 are removed from ACC-24E2A.

#### Acc-24E2A DAC-Torque/Velocity Mode

Acc-24E2A DAC - Sinusoidal Commutation Mode

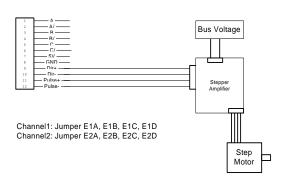

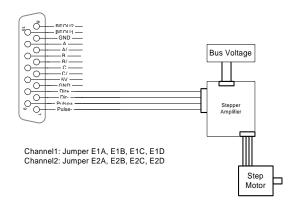

## **Stepper Drive, Pulse and Direction Outputs (TTL Level)**

#### Acc-24E2A PFM-Stepper Output

## **Amplifier Fault Inputs**

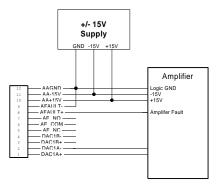

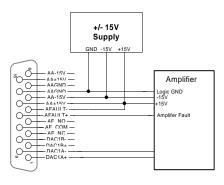

Sample diagrams shown below utilize a separate  $\pm 15V$  power supply for opto-isolation. E85, E87, and E88 are removed from ACC-24E2A.

#### Acc-24E2A Sinking Amplifier Fault

Acc-24E2A Sourcing Amplifier Fault

## **Amplifier Enable Outputs**

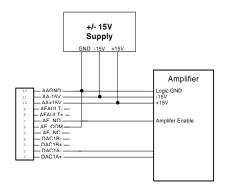

Sample diagrams shown below utilize a separate  $\pm 15V$  power supply for opto-isolation. E85, E87, and E88 are removed from ACC-24E2A.

#### Acc-24E2A Normally Open Amplifier Enable

Acc-24E2A Normally Closed Amplifier Enable

### **SOFTWARE SETUP**

## **Using ACC-24E2A with UMAC Turbo**

#### **Servo IC Numbering**

The Servo IC I-variables in ACC-24E2A are addressed with I7m00-I7m99 for servo IC m and channel n (where m=2 to 9 ). The number m of the Servo IC on the ACC-24E2A board is dependent on the addressing of the board with DIP switches S1-1, S1-3, and S1-4, which place the board as the first through eight external devices:

| • |               | First ACC-24E2 with Option 1:   | Servo IC 2 (channels 1- |

|---|---------------|---------------------------------|-------------------------|

| • | 4)            | Second ACC-24E2 with Option 1   | Servo IC 3 (channels 5- |

| • | 8)            | Third ACC-24E2 with Option 1:   | Servo IC 4 (channels 9- |

| • | 12)<br>13-16) | Fourth ACC-24E2 with Option 1   | Servo IC 5 (channels    |

| • | 17-20)        | Fifth ACC-24E2 with Option 1:   | Servo IC 6 (channels    |

| • | 21-24)        | Sixth ACC-24E2 with Option 1    | Servo IC 7 (channels    |

| • | 25-28)        | Seventh ACC-24E2 with Option 1: | Servo IC 8 (channels    |

| • | 29-32)        | Eighth ACC-24E2 with Option 1   | Servo IC 9 (channels    |

|   | 49-34)        |                                 |                         |

The Standard Servo IC on an ACC-24E2A occupies Channels 1-2 on the board, using connectors associated with channels 1 and 2. The Option 1 on an ACC-24E2A occupies Channels 3-4 on the board, using connectors associated with channels 3 and 4.

**Example:** The Standard Servo IC on the first ACC-24E2 is Servo IC 2 to Turbo PMAC and is configured by variables I7200 – I7299.

### **Servo Channel Numbering**

Each Servo IC has four channels of servo interface circuitry. The tens digit n of the I-variable configuring the IC represents the channel number on the IC (n = 1 to 4). For example, Channel 1 of the Standard Servo IC on the first ACC-24E2A is configured by variables I7210 – I7219. These channel-specific I-variables are represented generically as I7mn0 – I7mn9, where m represents the Servo IC number (2-9) and n represents the IC channel number (1-4).

The Channels 1-4 on the Standard Servo IC of an ACC-24E2A correspond to Channels 1-4, respectively, on the ACC-24E2A board itself.

I-variables in the I7000s for which the tens digit is 0 (Channel 0) affect all four channels of the PMAC2-style Servo IC on the ACC-24E2A. These multi-channel I-variables are represented generically as I7m00 – I7m09.

#### **Multi-Channel I-Variables**

Several multi-channel I-variables must be set up for proper operation of the ACC-24E2A in a Turbo PMAC system. The most important are:

I7m07: Servo IC m Phase/Servo Clock Direction

This variable should be set to 0 on the ACC-24E2A generating the clocks.

I7m00: Servo IC m MaxPhase/PWM Frequency Control

Typically, this will be set to the same value as the variable that controls the system clocks: I7200 on a UMAC Turbo PMAC2. If a different PWM frequency is desired then the following constraint should be observed in setting this variable:

$$\frac{2*PWMFreq(kHz)}{PhaseFreq} = \{ Integer \}$$

I7m01: Servo IC m Phase Clock Frequency Control

Even though the IC is receiving an external phase clock (see I7m07, above), usually it is best to create the same internal phase clock frequency in the Servo IC. This yields the following constraint:

$$17m00*(17m01+1) = 17200*(17201+1)$$

{UMAC Turbo}

Solving for I7m01, we get

$$I7m01 = \frac{I7200 * (I7201 + 1)}{I7m00} - 1$$

{UMAC Turbo}

If I7m00 is the same as I7200, I7m01 will be the same as I7201.

I7m02: Servo IC m Servo Clock Frequency Control

Even though the IC is receiving an external servo clock (see I7m07, above), usually it is best to create the same internal servo clock frequency in the Servo IC. This means that I7m02 for the IC should be set the same as I7202 on a UMAC Turbo.

I7m03: Servo IC m Hardware Clock Frequency Control

The hardware clock frequencies for the Servo IC should be set according to the devices attached to it. There is no reason that these frequencies have to be the same between ICs. There is seldom a reason to change this value from the default.

#### **Single-Channel I-Variables**

The single-channel setup I-variables for Channel n of Servo IC m work the same on an ACC-24E2 as they do on a Turbo PMAC2 itself. Each Servo IC has four channels n, numbered 1 to 4. For the first (standard) Servo IC on the ACC-24E2, the channel numbers 1-4 on the Servo IC are the same as the channel numbers 1-4 on the board. The most important variables are:

I7mn0: Servo IC m Channel n Encoder Decode Control

Typically, I7mn0 is set to 3 or 7 for x4 quadrature decode, depending on which way is up. If the channel is used for open-loop stepper drive, I7mn0 is set to 8 to accept internal pulse-and-direction, or to 0 to accept external pulse-and-direction (e.g. from an ACC-8S). It is set to 12 if the channel is used for MLDT feedback.

I7mn2: Servo IC m Channel n Capture Control

I7mn2 determines whether the encoder index channel, an input flag, or both, are used for the capture of the encoder position.

I7mn3: Servo IC m Channel n Capture Flag Select

I7mn3 determines which input flag is used for encoder capture, if one is used.

I7mn6: Servo IC m Channel n Output Mode Select

I7mn6 determines whether the A and B outputs are DAC or PWM, and whether the C output is PFM (pulse-and-direction) or PWM. Typically, it is set to 0, for 3-phase PWM, or to 3 for DACs and PFM.

#### **Encoder Conversion Table I-Variables**

To use feedback or master position data from an ACC-24E2A, add entries to the encoder conversion table (ECT) using I-variables I8000 – I8191 to address and process this data. The default conversion table in the Turbo PMAC does not contain these entries; it only contains entries for the eight channels on board the Turbo PMAC. The ECT entries for ACC-24E2 incremental encoder channels are shown in the following table:

| Servo IC # | Chan. 1  | Chan. 2  | Chan. 3  | Chan. 4  | Notes                                   |

|------------|----------|----------|----------|----------|-----------------------------------------|

| 2          | \$m78200 | \$m78208 | \$m78210 | \$m78218 | First ACC-24E2x Channel n Encoder Set   |

| 3          | \$m78300 | \$m78308 | \$m78310 | \$m78318 | Second ACC-24E2x Channel n Encoder Set  |

| 4          | \$m79200 | \$m79208 | \$m79210 | \$m79218 | Third ACC-24E2x Channel n Encoder Set   |

| 5          | \$m79300 | \$m79308 | \$m79310 | \$m79318 | Fourth ACC-24E2x Channel n Encoder Set  |

| 6          | \$m7A200 | \$m7A208 | \$m7A210 | \$m7A218 | Fifth ACC-24E2x Channel n Encoder Set   |

| 7          | \$m7A300 | \$m7A308 | \$m7A310 | \$m7A318 | Sixth ACC-24E2x Channel n Encoder Set   |

| 8          | \$m7B200 | \$m7B208 | \$m7B210 | \$m7B218 | Seventh ACC-24E2x Channel n Encoder Set |

| 9          | \$m7B300 | \$m7B308 | \$m7B310 | \$m7B318 | Eighth ACC-24E2x Channel n Encoder Set  |

The first hexadecimal digit in the entry, represented by m in the table, is a 0 for the most common 1/T timer-based extension of digital incremental encoders; it is an 8 for the parallel-data extension of analog incremental encoders; it is a C for no extension of an incremental encoder.

#### **Motor Addressing I-Variables**

For a Turbo PMAC motor to use the servo interface circuitry of the ACC-24E2, several of the addressing I-variables for the motor must contain the addresses of registers in the ACC-24E2, or the addresses of encoder conversion table registers containing data processed from the ACC-24E2. These I-variables can include:

Ixx02: Motor xx Command Output Address

Ixx02 tells Turbo PMAC where to write its command outputs for Motor xx. If ACC-24E2 is to create the command signals, Ixx02 must contain the address of the register.

The following table shows the address of the A output register for each channel of each ACC-24E2. These addresses can be used for single analog outputs, double analog outputs, or direct PWM outputs.

| Servo IC # | Chan. 1  | Chan. 2  | Chan. 3  | Chan. 4  | Notes                                |

|------------|----------|----------|----------|----------|--------------------------------------|

| 2          | \$078202 | \$07820A | \$078212 | \$07821A | First ACC-24E2x Channel n DAC/PWMnA  |

| 3          | \$078302 | \$07830A | \$078312 | \$07831A | Second ACC-24E2x Channel n           |

|            |          |          |          |          | DAC/PWMnA                            |

| 4          | \$079202 | \$07920A | \$079212 | \$07921A | Third ACC-24E2x Channel n DAC/PWMnA  |

| 5          | \$079302 | \$07930A | \$079312 | \$07931A | Fourth ACC-24E2x Channel n DAC/PWMnA |

| 6          | \$07A202 | \$07A20A | \$07A212 | \$07A21A | Fifth ACC-24E2x Channel n DAC/PWMnA  |

| 7          | \$07A302 | \$07A30A | \$07A312 | \$07A31A | Sixth ACC-24E2x Channel n DAC/PWMnA  |

| 8          | \$07B202 | \$07B20A | \$07B212 | \$07B21A | Seventh ACC-24E2x Channel n          |

|            |          |          |          |          | DAC/PWMnA                            |

| 9          | \$07B302 | \$07B30A | \$07B312 | \$07B31A | Eighth ACC-24E2x Channel n DAC/PWMnA |

If the C output register for a given ACC-24E2 and channel is used (primarily for pulse and direction output), simply add 2 to the address shown in the above table. For example, on the first ACC-24E2, output register 1C is at address \$078204.

Ixx03: Motor xx Position-Loop Feedback Address Ixx04: Motor xx Velocity-Loop Feedback Address

Ixx05: Motor xx Master Position Address

Usually, the Ixx03, Ixx04, and Ixx05 variables contain the address of a processed position value in the encoder conversion table, even when the raw data comes from the ACC-24E2A. The first line of the encoder conversion table is at address \$003501; the last line is at address \$0035C0.

Ixx10: Motor xx Power-On Position Address

Ixx10 tells the Turbo PMAC where to read absolute power-on position, if any. Typically, the only times Ixx10 will contain the address of an ACC-24E2A register is if the position is obtained from an A/D converter on an ACC-28B connected through the ACC-24E2A, or if it is obtained from an MLDT (e.g. Temposonics<sup>TM</sup>) sensor excited directly from an ACC-24E2A.

The following table shows the possible values of Ixx10 for MLDT timer registers:

Ixx10 for ACC-24E2 MLDT Timer Registers (Ixx95=\$170000)

| Servo IC # | Chan. 1  | Chan. 2  | Chan. 3  | Chan. 4  | Notes                             |

|------------|----------|----------|----------|----------|-----------------------------------|

| 2          | \$078200 | \$078208 | \$078210 | \$078218 | First ACC-24E2x Channel n Timer   |

| 3          | \$078300 | \$078308 | \$078310 | \$078318 | Second ACC-24E2x Channel n Timer  |

| 4          | \$079200 | \$079208 | \$079210 | \$079218 | Third ACC-24E2x Channel n Timer   |

| 5          | \$079300 | \$079308 | \$079310 | \$079318 | Fourth ACC-24E2x Channel n Timer  |

| 6          | \$07A200 | \$07A208 | \$07A210 | \$07A218 | Fifth ACC-24E2x Channel n Timer   |

| 7          | \$07A300 | \$07A308 | \$07A310 | \$07A318 | Sixth ACC-24E2x Channel n Timer   |

| 8          | \$07B200 | \$07B208 | \$07B210 | \$07B218 | Seventh ACC-24E2x Channel n Timer |

| 9          | \$07B300 | \$07B308 | \$07B310 | \$07B318 | Eighth ACC-24E2x Channel n Timer  |

Ixx24: Motor xx Flag Mode

Ixx24 defines how to read and use the flags for Motor xx that are in the register specified by Ixx25. Ixx24 is a set of independent control bits. There are two bits that must be set correctly to use a flag set on an ACC-24E2.

Bit 0 of Ixx24 must be set to 1 to tell the Turbo PMAC that this flag set is in a Type 1 PMAC2-style Servo IC. Bit 18 of Ixx24 must be set to 0 to tell the Turbo PMAC that this flag set is not transmitted over a MACRO ring. Other bits of Ixx24 may be set as desired for a particular application.

See Turbo PMAC Software Reference Manual for description of Ixx24.

Ixx25: Motor xx Flag Address

Ixx25 tells Turbo PMAC where to access its flag data for Motor xx. If ACC-24E2 is interfaced to the flags, Ixx25 must contain the address of the flag register in ACC-24E2. The following table shows the address of the flag register for each channel of each ACC-24E2.

| Servo IC # | Chan. 1  | Chan. 2  | Chan. 3  | Chan. 4  | Notes                                |

|------------|----------|----------|----------|----------|--------------------------------------|

| 2          | \$078200 | \$078208 | \$078210 | \$078218 | First ACC-24E2x Channel n Flag Set   |

| 3          | \$078300 | \$078308 | \$078310 | \$078318 | Second ACC-24E2x Channel n Flag Set  |

| 4          | \$079200 | \$079208 | \$079210 | \$079218 | Third ACC-24E2x Channel n Flag Set   |

| 5          | \$079300 | \$079308 | \$079310 | \$079318 | Fourth ACC-24E2x Channel n Flag Set  |

| 6          | \$07A200 | \$07A208 | \$07A210 | \$07A218 | Fifth ACC-24E2x Channel n Flag Set   |

| 7          | \$07A300 | \$07A308 | \$07A310 | \$07A318 | Sixth ACC-24E2x Channel n Flag Set   |

| 8          | \$07B200 | \$07B208 | \$07B210 | \$07B218 | Seventh ACC-24E2x Channel n Flag Set |

| 9          | \$07B300 | \$07B308 | \$07B310 | \$07B318 | Eighth ACC-24E2x Channel n Flag Set  |

#### **TURBO UMAC Example Setups**

The following section shows how to quickly setup the key variables for a DAC output system and for a combination torque mode (DAC) and stepper motor (PFM) system.

For these examples, the factory defaults for the other variables will allow the command of DAC outputs and PFM outputs with a low true Amplifier Fault and ±Limits plugged in. If this is not the case then Ixx24 will have to be modified. The PID gains will also have to be modified for optimum closed loop control.

**Example A:** Setup the first 4 motors as DAC outputs on first ACC-24E2A in UMAC Turbo:

```

1100.4.100=1

; Motor 1-4 enabled

I102=$78202

; Command output to CH1A address (PMAC default) for DAC

I202=$7820A

; Command output to CH2A address (PMAC default) for DAC

I302=$78212

; Command output to CH3A address (PMAC default) for DAC

I402=$7821A

; Command output to CH4A address (PMAC default) for DAC

17216,4,10=1

; Servo IC 2 CHn 1-4 output mode select

; Low True Amplifier Fault and enable hard limits

I124,4,100=$800001

I8000=$78200

; Encoder Convertion Table entries for 1/T extension (PMAC Default)

I8001=$78208

T8002=$78210

I8003=$78218

I103,2,1=$3501

; Pos/Vel feedback pointing to first 4 ECT entries (PMAC Default)

I203,2,1=$3502

I303,2,1=$3503

I403,2,1=$3504

```

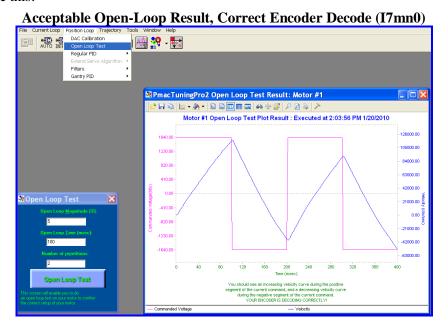

After this initial setup, we can use tuning software to perform open loop test. The result of open loop test should look like this:

After a successful open loop test, PID tuning should be performed by the user.

# **Example B:** Setup the first 4 motors as Step and Direction outputs on first ACC-24E2A in UMAC Turbo (Stepper Motor):

```

I100,4,100=1

; Motor 1-4 enabled

I102=$78204

; Command output to CH1C address for {\tt PFM}

I202=$7820C

; Command output to CH1C address for PFM

I302=$78214

; Command output to CH1C address for PFM

I402=$7821C

; Command output to CH1C address for PFM

I7216,4,10=1

; Servo IC 2 CHn 1-4 output mode select

I124,4,100=$800001

; Low True Amplifier Fault and enable hard limits

I8000=$78200

; Encoder Convertion Table entries for 1/T extension

I8001=$78208

I8002=$78210

I8003=$78218

I103,2,1=$3501

; Position and Velocity feedback pointing to first 4 ECT entries

I203,2,1=$3502

I303,2,1=$3503

I403,2,1=$3504

```

### Using ACC-24E2A with ULTRALITE/MACRO STATION

#### Clocks and Strobe Word

All MACRO Communication variables on the Master such as I6840/I6890/I6940/I6990, I6841/I6891/I6941/I6991, I78,I70~I77,I80,I81,I82 and on the station such as MI996,MI995 are assumed to be set correctly before configuring ACC-24E2A. For more information on how to set these variables look the User Manual for your Master (UltraLite/UMAC with ACC-5E) and MACRO 16 CPU.

There are several choices when it comes to the software setup for the MACRO Station. At the MACRO Station the ring frequency must be set up with MSn,MI992. The ACC-24E2A will have its MaxPhase Clock Frequency variables (MSn,MI900 and MSn,MI906) set to the same value as MSn,MI992 to ensure synchronous data exchange. The Delta Tau Setup software for either the standard PMAC2 Ultralite or Turbo PMAC2 Ultralite will set up all of these important MI-Variables at the MACRO Station. The ACC-24E2A uses an 18-bit DAC and the DAC Strobe word (MSn,MI905 and MSn,MI909) must be setup for 18-bits to ensure proper operation of the DACs.

MS{anynode},MI992 - Ring Frequency Control

MS{anynode},MI900 - Channels 1-4 Frequency Control

MS{anynode},MI905 - DAC 1-4 Strobe Word

MS{anynode},MI906 - Channels 5-8 Frequency Control

MS{anynode},MI909 - DAC 5-8 Strobe Word

The released MACRO Station firmware version 1.14 will set the DAC strobe variables automatically. In pre-release versions of the 1.14 firmware, the DAC strobe word must be set manually to \$7FFFC0 for proper 18-bit DAC operation.

### **Node-Specific Gate Array MI-Variables**

MI-variables MI910 through MI919 on the MACRO station control the hardware setup of the hardware interface channel on the station associated with a MACRO node. The matching of hardware interface channels to MACRO nodes is determined by the setting of the SW1 rotary switch on the CPU/Interface Board of the MACRO station.

These variables are accessed using the MS station auxiliary read and write commands. The number immediately after the MS specifies the node number, and therefore the channel number mapped to that node by the SW1 setting.

#### Encoder/Timer n Decode Control (MSn,MI910)

MI910 controls how the input signal for the encoder mapped to the specified node is decoded into counts. As such, this defines the sign and magnitude of a count. The following settings may be used to decode an input signal:

- 0: Pulse and direction CW

- 1: x1 quadrature decode CW

- 2: x2 quadrature decode CW

- 3: x4 quadrature decode CW

- 4: Pulse and direction CCW

- 5: x1 quadrature decode CCW

- 6: x2 quadrature decode CCW

- 7: x4 quadrature decode CCW

- 8: Internal pulse and direction

- 9: Not used

- 10: Not used

- 11: Not used

- 12: MLDT pulse timer control (internal pulse resets timer; external pulse latches timer)

- 13: Not used

- 14: Not used

- 15: Not used

In any of the quadrature decode modes, PMAC is expecting two input waveforms on CHAn and CHBn, each with approximately 50% duty cycle, and approximately one-quarter of a cycle out of phase with each other. Times-one (x1) decode provides one count per cycle; x2 provides two counts per cycle; and x4 provides four counts per cycle. Select x4 decode to get maximum resolution.

The clockwise (CW) and counter clockwise (CCW) options simply control which direction counts up. If it is the wrong direction sense, simply change to the other option (e.g., from 7 to 3 or vice versa).

If the direction sense of an encoder with a properly working servo is changed without also changing the direction sense of the output, destabilizing positive feedback to the servo and a dangerous runaway condition will result.

In the pulse-and-direction decode modes, PMAC is expecting the pulse train on CHAn and the direction (sign) signal on CHBn. If the signal is unidirectional, the CHBn line can be allowed to pull up to a high state, or it can be hardwired to a high or low state.

If MI910 is set to 8, the decoder inputs the pulse and direction signal generated by Channel n's pulse frequency modulator (PFM) output circuitry. This permits the Compact MACRO Station to create a phantom closed loop when driving an open-loop stepper system. No jumpers or cables are needed to do this; the connection is entirely within the ASIC. The counter polarity matches the PFM output polarity automatically.

If MI910 is set to 12, the timer circuitry is set up to read magnetostrictive linear displacement transducers (MLDTs) such as Temposonics<sup>TM</sup>. In this mode, the timer is cleared when the PFM circuitry sends out the excitation pulse to the sensor on PULSEn, and it is latched into the memory-mapped register when the excitation pulse is received on CHAn.

#### Flag Capture Control (MSn,MI911-MI913)

The flag capture registers must also be set up at the MACRO Station for proper homing, encoder capturing, and setting compare outputs.

MI911 determines which encoder input the position compare circuitry for the machine interface channel mapped to the specified node uses.

MSn, MI 911=0 Use channel n encoder counter for position compare function

MSn, MI 911=1 Use first encoder counter on IC (encoder 1 for channels 1 to 4; encoder 5 for channels 5 to 8) for position compare function

When MI911 is set to 0, the channel's position compare register is tied to the channel's own encoder counter, and the position compare signal appears only on the EQUn output.

When MI911 is set to 1, the channel's position compare register is tied to the first encoder counter on the ASIC (Encoder 1 for channels 1-4, Encoder 5 for channels 5-8, or Encoder 9 for channels 9-10) and the position compare signal appears both on EQUn and combined into the EQU output for the first channel on the IC (EQU1 or EQU5); executed as a logical OR.

MI911 for the first channel on an ASIC performs no effective function, so is always 1. It cannot be set to 0.

MI912 determines which signal or combination of signals, and which polarity, triggers a position capture of the counter for the encoder mapped to the specified node. If a flag input (home, limit, or user) is used, MI913 for the node determines which flag. Proper setup of this variable is essential for a successful home search, which depends on the position-capture function. The following settings may be used:

- 0: Capture under software control (armed)

- 1: Capture on Index (CHCn) high

- 2: Capture on Flag high

- 3: Capture on (Index high AND Flag high)

- 4: Capture under software control (latched)

- 5: Capture on Index (CHCn) low

- 6: Capture on Flag high

- 7: Capture on (Index low AND Flag high)

- 8: Capture under software control (armed)

- 9: Capture on Index (CHCn) high

- 10: Capture on Flag low

- 11: Capture on (Index high AND Flag low)

- 12: Capture under software control (latched)

- 13: Capture on Index (CHCn) low

- 14: Capture on Flag low

- 15: Capture on (Index low AND Flag low)

The trigger is armed when the position capture register is read. After this, as soon as the MACRO Station sees that the specified input lines are in the specified states, the trigger will occur — it is level-trigger, not edge-triggered.

**MI913** parameter determines which of the Flag inputs will be used for position capture (if one is used, see MI912):

- 0: HMFLn (Home Flag n)

- 1: PLIMn (Positive End Limit Flag n)

- 2: MLIMn (Negative End Limit Flag n)

- 3: USERn (User Flag n)

Typically, this parameter is set to 0 or 3, because in actual use the LIMn flags create other effects that usually interfere with what is trying to be accomplished by the position capture. To capture on the LIMn flags, disable their normal functions with Ix25, or use a channel n where none of the flags is used for the normal axis functions.

#### Output Mode Select (MSn,MI916)

The PMAC2 Style outputs allow the PMAC to control up to three individual output channels based on the mode. These outputs are described as output A, output B, and output C.

| MSn, MI916 | Output Description        | Typical Use                                                     |

|------------|---------------------------|-----------------------------------------------------------------|

| 0          | A, B, and C are PWM       | Direct PWM Mode Only                                            |

| 1          | A and B are DAC, C is PWM | ±10V Outputs for torque, velocity and sinusoid input amplifiers |

| 2          | A and B are PWM, C is PFM | Stepper Systems                                                 |

| 3          | A and B are DAC, C is PFM | ±10V Outputs with MLDT Feedback                                 |

#### DAC Output Mode Example for ACC-24E2A at MACRO Station

| MS0,MI916=3  | ; DAC | output | for | Channel | 1 |

|--------------|-------|--------|-----|---------|---|

| MS1,MI916=3  | ; DAC | output | for | Channel | 2 |

| MS4,MI916=3  | ; DAC | output | for | Channel | 3 |

| MS5,MI916=3  | ; DAC | output | for | Channel | 4 |

| MS8,MI916=3  | ; DAC | output | for | Channel | 5 |

| MS9,MI916=3  | ; DAC | output | for | Channel | 6 |

| MS12,MI916=3 | ; DAC | output | for | Channel | 7 |

| MS13,MI916=3 | ; DAC | output | for | Channel | 8 |

#### MACRO Station Encoder Conversion Table (MSn,MI120-MI151)

At power-up, the MACRO Station will set up all of the key memory locations and MI-Variables automatically based on the SW1 connector and firmware of the MACRO Station. The key variables set up at power-up are the encoder conversion table, servo output registers, and flag input registers. By default all encoder conversion table entries are set for 1/T of incremental encoder as:

```

MS0,MI120=$008000

;output at X:$0010 at MACRO Station (encoder 1)

MS0,MI121=$008008

;output at X:$0011 at MACRO Station (encoder 2)

MS0,MI122=$008010

;output at X:$0012 at MACRO Station (encoder 3)

MS0,MI123=$008018

;output at X:$0013 at MACRO Station (encoder 4)

;output at X:$0014 at MACRO Station (encoder 5)

MS0,MI120=$008040

MS0,MI121=$008048

;output at X:$0015 at MACRO Station (encoder 6)

MS0,MI122=$008050

;output at X:$0016 at MACRO Station (encoder 7)

MS0,MI123=$008058

;output at X:$0017 at MACRO Station (encoder 8)

MS1,MI120=$009000

;output at X:$0090 at MACRO Station (encoder 1)

MS1,MI121=$009008

;output at X:$0091 at MACRO Station (encoder 2)

MS1,MI122=$009010

;output at X:$0092 at MACRO Station (encoder 3)

MS1, MI123=$009018

;output at X:$0093 at MACRO Station (encoder 4)

MS1,MI120=$009040

;output at X:$0094 at MACRO Station (encoder 5)

MS1,MI121=$009048

;output at X:$0095 at MACRO Station (encoder 6)

MS1,MI122=$009050

;output at X:$0096 at MACRO Station (encoder 7)

MS1,MI123=$009058

;output at X:$0097 at MACRO Station (encoder 8)

```

For more information on how to setup encoder conversion table look at MACRO 16 User Manual.

### **Using ACC-24E2A with Power PMAC**

Much of the hardware on the ACC-24E2A is software configurable to provide the maximum flexibility. This section explains in detail the software setup for the Power PMAC CPU that is required to use the ACC-24E2A in different modes of operation.

When the Power PMAC is re-initialized using the \$\$\$\*\*\* command with ACC-24E2A in the rack, the most commonly used settings of the setup elements will be made automatically. Further, the hardware setup window in the Power PMAC IDE program will walk you through the setup of many of these elements. So for many users, this manual section will be primarily for reference. However, other users will want to know how to set up the board "manually".

#### **DSPGATE1 Servo IC Data Structure Elements**

The Power PMAC CPU communicates with the ACC-24E2A by accessing memory-mapped registers in the "DSPGATE1" Servo IC that was designed by Delta Tau to provide a sophisticated interface between controller software and system hardware. Settings of the control registers in this IC determine the software configuration of the ACC-24E2A for a particular application.

The Power PMAC has defined a "Gate1" data structure to organize the control and status settings of the ASIC. In the Script environment – either buffered program statements or on-line commands – a user can utilize this Gate1[i] data structure directly, or use its "alias" of the Acc24E2A[i] data structure. In C programs, the user must utilize the Gate1[i] data structure directly, although a "#define" substitution may be employed to get it. This manual will use the Gate1[i] name for maximum generality. Elements of the data structure that affect all servo channels are of the form:

#### Gate1[i].{element name}

The ASIC index number "i" has a valid range of 4 to 19 in the UMAC rack and corresponds to the setting of the addressing DIP switches on SW1 of the 3U-format base board. No two boards with the DSPGATE1 IC (ACC-24E2, ACC-24E2A, ACC-24E2S, ACC-51E) on a single backplane may have the same DIP switch setting; otherwise an addressing conflict will be created (Look at Hardware Setup Switch Configuration).

Elements of the data structure that affect only a single servo channel are of the form:

#### Gate1[i].Chan[j].{element name}

The channel index number "j" has a range of 0 to 3, corresponding to hardware channels 1 to 4, respectively, for the accessory. The index number for a channel is one less than the corresponding hardware channel number.

Channel index numbers 0 and 1 correspond to hardware channels 1 and 2, which are on the 3U-format base board, on the left side of a 4-channel assembly. Channel index numbers 2 and 3 correspond to hardware channels 3 and 4, which are on the 3U-format piggyback board, on the right side of a 4-channel assembly.

### **Software Setup for Clock Signals**

The clock frequencies of an ACC-24E2A are set by software data structure elements. Some of these clock frequencies can be used to control the entire Power PMAC system.

#### Phase and Servo Clock Direction

In a Power PMAC UMAC system, only one machine interface IC is the source of phase and servo clock signals for the entire system. This IC generates its own phase and servo clock signals and outputs them to the rest of the system over the UBUS backplane. The Power PMAC CPU uses these signals as interrupts to drive its phase-commutation and servo-loop algorithms, respectively. Other machine interface ICs use these clock signals to drive their own input and output functions.

On the re-initialization of a Power PMAC UMAC system, the CPU will automatically set up the lowest-numbered DSPGATE1 IC found as the source of the system clock signals. It does this by setting **Gate1[i].PhaseServoDir** for this IC to 0. It sets **Gate1[i].PhaseServoDir** for all of the other ICs it finds to 3, so they will input their phase and servo clock signals. (However, if any boards with DSPGATE2 or DSPGATE3 ICs are found, one of those boards will be used as the source of system clock signals and **Gate1[i].PhaseServoDir** for all of the boards with the DSPGATE1 IC will be set to 3 to input the clock signals.

### Phase Clock Frequency

The frequency of phase clock generated internally by the IC on an ACC-24E2A is determined by the settings of **Gate1**[*i*].**PwmPeriod** and **Gate1**[*i*].**PhaseClockDiv**. If this IC is the source of the phase clock for the system, this frequency will control the entire UMAC system, hardware and software.

**Gate1**[*i*].**PwmPeriod** controls the internal "MaxPhase" clock frequency (and the PWM frequency, which is not used) on the ACC-24E2A's "DSPGATE1" Servo IC. The internally generated Phase and Servo clocks on the IC are derived from the MaxPhase clock. It controls these frequencies by setting the limits of the PWM up-down counter, which increments and decrements at the PWMCLK frequency of 117,964.8 kHz (117.9648 MHz).

To set **Gate1**[i].**PwmPeriod** for a desired "maximum phase" clock frequency, the following formula can be used:

$$Gatel[i].PwmPeriod = \frac{117,964.8(kHz)}{2*MaxPhaseFeq(kHz)} - 3$$

or:

$$MaxPhaseFeq(kHz) = \frac{117,964.8(kHz)}{2*(Gatel[i].PwmPeriod+3)}$$

**Gate1**[i].**PwmPeriod** constitutes bits 8-23 of the full-word element **Gate1**[i].**PwmCtrl** (bits 16-31 of the 32-bit element in C).

**Gate1**[*i*].**PhaseClockDiv** controls how many times the Phase clock frequency is divided down from the "maximum phase" clock. The Phase clock frequency is equal to the "maximum phase" clock frequency divided by (**Gate1**[*i*].**PhaseClockDiv**+1). **Gate1**[*i*].**PhaseClockDiv** has a range of 0 to 15, so the frequency division can be by a factor of 1 to 16. The equation for **Gate1**[*i*].**PhaseClockDiv** is

Gatel[i].PhaseClocIDiv =

$$\frac{MaxPhaseFeq(kHz)}{PhaseFreq(kHz)} - 1$$

or:

$$PhaseFreq(kHz) = \frac{MaxPhaseFeq(kHz)}{(Gatel[i].PhaseCloctDiv+1)}$$

**Gate1**[*i*].**PhaseClockDiv** constitutes bits 16 – 19 of the full-word element **Gate1**[*i*].**ClockCtrl** (bits 24 – 27 of the 32-bit element in C).

#### Servo Clock Frequency

Gate1[i].ServoClockDiv sets the internally generated servo clock frequency for the IC by specifying how many times the frequency is divided down from the phase clock frequency. It has a range of 0 to 15, specifying a division factor of 1 to 16, respectively. The equation for **Gate1[i].ServoClockDiv** is:

$$Gatel[i].ServoCloclDiv = \frac{PhaseFre(kHz)}{ServoFre(kHz)} - 1$$

or: